F28XX: Write-Followed-by-Read Pipeline Protection

Write-Followed-by-Read Pipeline Protection. Taken from document spru067c.pdf ( spru949a.pdf for F28335 ) by Texas Instruments.

In the 28x CPU pipeline, the read phase of an operation occurs before the write phase. Due to this ordering, a write followed by a read access can actually occur in the opposite order: read followed by write.

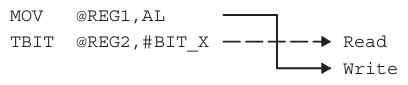

For example, the following lines of code perform a write to one location followed by a read from another. Due to the 28x CPU pipeline, the read operation will be issued before the write as shown:

On 28x devices, regions of memory where peripheral registers are common

are protected from this order reversal by hardware. These regions of memory

are said to be read-followed-by-write pipeline protected. On the 2812 devices,

XINTF Zone 1 (XINTF Zone 0 for F28335) is by default read-followed-by-write pipeline protected. Write

and read accesses to Zone 1 (Zone 0 for F28335) get executed in the same order they are written.

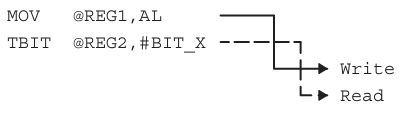

For example, a write followed by a read is executed in the same order it was

written as shown below:

The 28x CPU automatically protects writes followed by reads to the same

memory location. The protection mechanism described above is for cases

where the address is not the same, but within a given region of protected

memory. In this case, the order of execution is preserved by the CPU

automatically inserting enough NOP cycles for the write to complete before the

read occurs.

This execution ordering becomes a concern only when peripherals are mapped to the XINTF. A write to one register may update status bits in another register. In this case, the write to the first register needs to be complete before the read to the second register takes place. If the write and read operations are performed in the natural pipeline order, the wrong status may be read since the write would happen after the read. This reversal is not a concern when memory is mapped to the XINTF. XINTF Zone 1 (XINTF Zone 0 for F28335) includes the write-followed-by-read protection by default and the CPU automatically adds required cycles between writes followed by reads. Thus, Zone 1 (Zone 0 for F28335) would typically not be used to access memory but instead would be used only to access external peripherals. If other zones other then Zone 1 (Zone 0 for F28335) are used to access peripherals that require the order write-followed-by-read instructions to be preserved, the following solutions can be used:

- Add up to 3 NOP assembly instructions between a write and read instructions. Fewer then 3 can be used if the code is analyzed and it is found that the pipeline stalls for other reasons.

- Move other instructions before the read to make sure that the write and read are at least three CPU cycles apart.

- Use the -mv compiler option to automatically insert NOP assembly instructions between write and read accesses. This option should be used with caution because this out-of-order execution is a concern only when accessing peripherals mapped to XINTF and not normal memory accesses.